## Distribution of Timing: Basics principle and Sync over the Physical Layer

#### Contents

- —The use of inclusive terminology

- -1.General

- 1.1 Time vs. Frequency

- 1.2 Master-Slave vs. Plesiochronous

- —1.3 Fundamental technologies and timing protocols

- 2. Frequency Sync over the Physical Layer

- -2.1 Introduction

- −2.2 SyncE

- -2.3 OTN

- Managing Synchronization in the Network

#### **Credits:**

Figures in slides 6, 9, 15 taken from book «Synchronous Ethernet and IEEE 1588 in Telecoms: Next Generation Synchronization Networks» (Wiley, 2013, ISBN: 978-1-848-21443-9)

#### The use of Inclusive Terminology

- IEEE Std 1588g-2022 Amendment to IEEE 1588 for inclusive terminology

- Scope "This amendment adds an optional alternative suitable and inclusive terminology to the terms: "master" and "slave", but it does not replace the terms "master" and "slave"."

- timeTransmitter and timeReceiver were selected as an alternative nomenclature for master and slave, and it has been used as a basis for the draft amendment

- IEEE Std 1588g-2022 was published last year and it is available via IEEE Standard Association (SA)

- IEEE Std 802.1ASdr-2024 IEEE 802.1 TSN has published an amendment to IEEE Std 802.1AS to replace non-inclusive terminology in the standard, it is based on IEEE Std 1588g-2022

- IEEE P3400 WG

- IEEE P3400 Standard for Use of Inclusive Language in Technical Terminology and Communications

- This standard is going through SA ballot

- ITU-T has almost completed revision of terminology of the active Recommendations

- Revision of terminology of Physical Layer (SyncPHY) has also been addressed

- Master and Slave are still used in slide 6 of this presentation

## 1. General

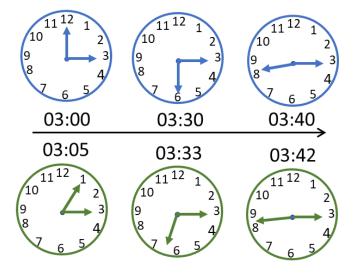

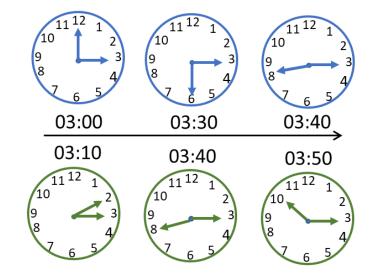

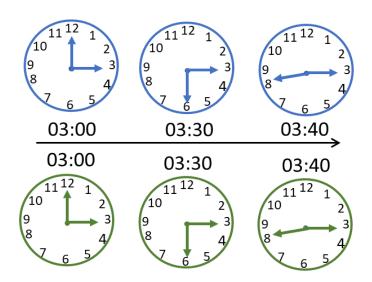

## Time vs Frequency

#### Not Synchronized

#### Frequency Synchronized (Syntonized)

#### Time/Phase/Frequency Synchronized

Credits: Figures based on book «Synchronous Ethernet and IEEE 1588 in

Telecoms: Next Generation Synchronization Networks»

(Wiley, 2013, ISBN: 978-1-848-21443-9)

#### Master-Slave vs. Plesiochronous

- Original focus in Telecom is **Frequency synchronization**. Basic concepts defined in ITU-T G.810:

- plesiochronous mode: A mode where the essential characteristic of time scales or signals such that their corresponding significant instants occur at nominally the same rate, any variation in rate being constrained within specified limits

- master slave mode: A mode where a designated master clock is used as a frequency standard which is

disseminated to all other clocks which are slaved to the master clock

- mutually synchronized mode: A mode where all clocks exert a degree of control on each other

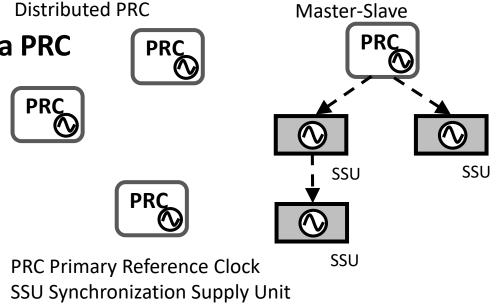

#### Telecom networks were originally synchronized to a PRC

- PRC were originally based on Cesium technology

- Timing Distribution based on Centralized architectures (based on synchronized mode)

- Increased use of GNSS-based sync leading to a mix of «Distributed PRC» and «synchronized mode»

- Renewed interest on Mutually Synchronized mode in the time sync domain

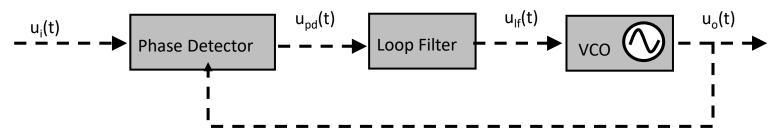

## Basic Technologies: GNSS, Atomic clocks, PLL

- —Phase locked loops (PLLs) can be used to form a synchronization chain from a timing source to a timing receiver to deliver time to an end application

- —Origin of time in the network :

- —GNSS Receivers

- Atomic Clocks (Cesium for frequency accuracy better than 10<sup>-11</sup>)

$u_i(t)$  input reference timing signal  $u_o(t)$  output reference timing signal  $u_{pd}(t)$  loop filter output signal  $u_{if}(t)$  phase detector output signal

#### **Timing Protocols**

#### —NTP, Network Time Protocol defined by IETF

- protocol for clock synchronization between computer systems over packet-switched networks

- —RFC 1305 (NTP version 3) 1992

- Latest version v4

- RFC 5905: Network Time Protocol Version 4: Protocol and Algorithms Specification

- RFC 5906: Network Time Protocol Version 4: Autokey Specification

- RFC 5907: Definitions of Managed Objects for Network Time Protocol Version 4 (NTPv4)

- RFC 5908: Network Time Protocol (NTP) Server Option for DHCPv6

#### —PTP, Precision Timing Protocol, defined by IEEE 1588

- -V1 (2002)

- -V2(2008)

- -V2.1(2019)

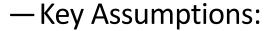

#### **How NTP Works**

- —T1 Originate Timestamp

- Time request sent by client

- —T2 Receive Timestamp

- Time request received by server

- —T3 Transmit Timestamp

- Time reply sent by server

- —T4 Destination Timestamp

- Time reply received by client

- Round Trip Delay=(T4-T1)-(T3-T2)

- Round Trip Delay =25-10=15

- Clock Offset= [(T2-T1)-(T4-T3)]/2

- Clock Offset =[5-10]/2= -2.5

(Clients actual time when reply received was therefore 09:00:0225)

- One way delay is half Round Trip (symmetry!)

- Drift of client and server clocks are small and close to same value

- Time is traceable

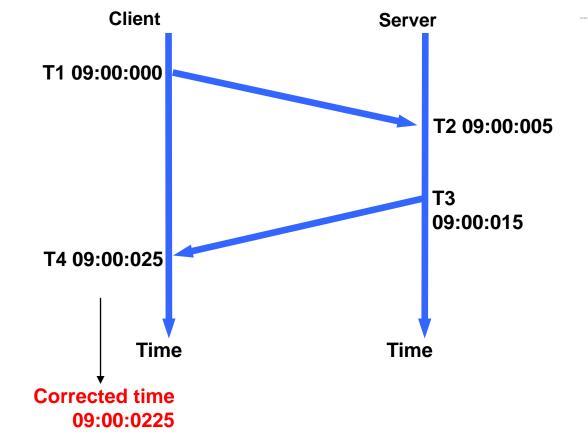

#### IEEE 1588-2008/2019

- —The Grandmaster "reference clock" sends a series of time-stamped messages

- timeReceiver process timestamps and synchronize to the Grandmaster.

- Frequency can be recovered from an accurate time of day reference (but physical layer can also be used )

- Best Master Clock Algorithm is used to define the synchronization hierarchy

- Accuracy is possible by means of:

- Proper packet rate (up to 128 per second)

- Hardware time-stamping (eliminate software processing delays)

- Timing support in the network

(e.g. transparent clocks, boundary clocks)

- New features in 2019:

- Addition of special ports to allow some technologies (e.g. WiFi and EPON) to use their inherent timing support

- New optional features (e.g. cumulative rate ratio, performance monitoring)

- High accuracy profile

- Security options

PTP control messages over valid network path

Clock reference

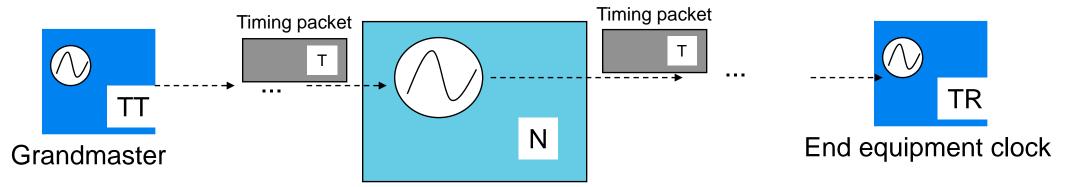

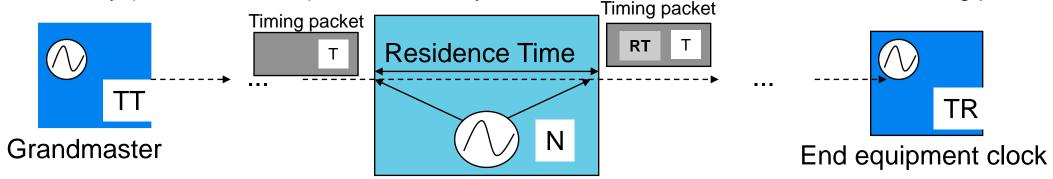

#### **Timing Support**

Timing packets are terminated and regenerated by Node N

e.g. IEEE1588 Boundary Clock, NTP Stratum Clock

Latency (Residence Time) is calculated by NE and the information is added in the timing packet

e.g. IEEE1588 Transparent Clock

To remove (reduce) «Time Error» components internal to the nodes

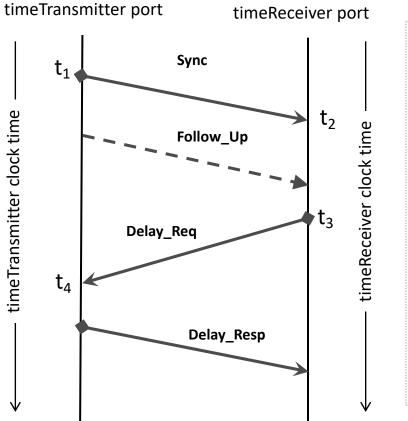

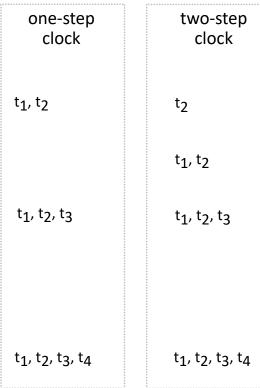

#### PTP Time Transfer Technique

#### Timestamps known by

#### Offset:

(timeReceiver clock error and one-way path delay)

$$Offset_{SYNC} = t2 - t1$$

$$Offset_{DELAY\ REQ} = t4 - t3$$

We assume path symmetry, therefore

Mean Path Delay =

$$[(t2 - t1) + (t4 - t3)] \div 2$$

timeReceiver Clock offset =  $[(t2 - t1) - (t4 - t3)] \div 2$

#### Notes:

- 1. One-way delay cannot be calculated exactly, but there is a bounded error.

- The protocol transfers TAI (Atomic Time).

UTC time is TAI + leap second offset from the announce message.

#### The concept of Profile

- A profile is a subset of required options, prohibited options, and the ranges and defaults of configurable attributes

- —e.g. for Telecom: Update rate, unicast/multicast, etc.

- —PTP profiles are created to allow organizations to specify selections of attribute values and optional features of PTP that, when using the same transport protocol, inter-works and achieve a performance that meets the requirements of a particular application

- —Telecom Profiles: G.8265.1, G.8275.1, G.8275.2

- —Other (non-Telecom) profiles:

- IEEE C37.238 (Standard Profile for Use of IEEE 1588 Precision Time Protocol in Power System Applications,)

- IEEE 802.1AS (Timing and Synchronization for Time-Sensitive Applications in Bridged Local Area Networks)

# 2. Frequency sync over the Physical layer

#### Introduction

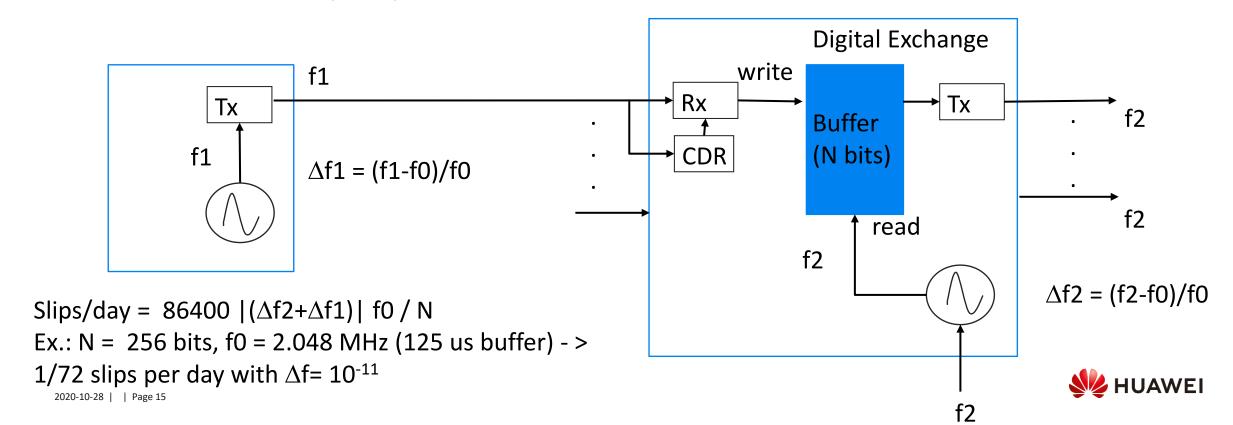

- Frequency distribution required originally in PDH / SDH-based networks

- To control the Slip rate (in circuit-switched networks) and control of jitter/wander in SDH networks

- Timing carried by the bit rate of the traffic signal (typically extracted by the frame alignment word in a TDM frame)

- —Slip: «The repetition or deletion of a block of bits in a synchronous or plesiochronous bit stream due to a discrepancy in the read and write rates at a buffer.» (G.810)

#### Basic principles

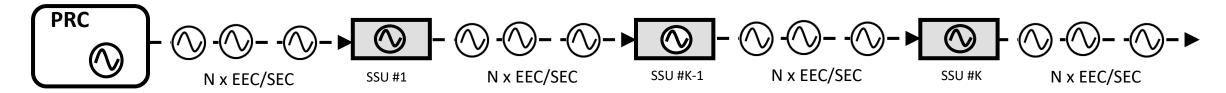

—G.803 specifies the reference chain as a combination of this clocks, that can guarantee to meet specified performance objectives

Worst case scenario calculation purposes:

K=10 and N= 20, with limitation that total number of clocks is less than 60

- Clocks have been specified in ITU-T G.812 and G.813

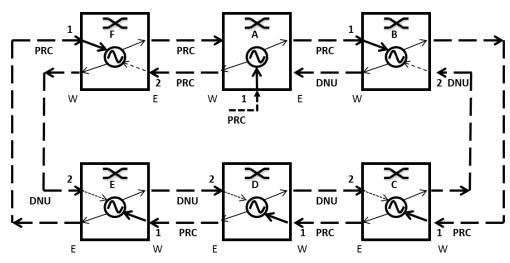

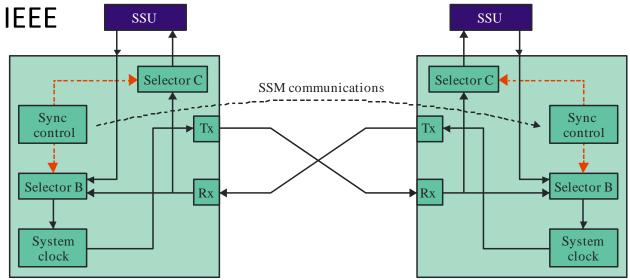

- G.781 specifies the synchronization function layer, including the basics for use of the Synchronization Status Message (SSM)

- To avoid timing loops (DNU = Do Not Use !)

- To inform downstream clocks when traceability is lost

- G.781 provides encoded QL values (PRC, SSU, SEC..)

## Intra/Inter-Station (Node)

— G.781 defines basic synchronization architectures — Timing distributed within a building (star topology) **PRC** — Timing distributed between buildings (tree) NodeClock > NodeClock \ (SSU) (SSU) Network Element Clock SEC/EEC) NodeClock NodeClock NodeClock NodeClock (SSU) (SSU) (SSU) Network Element Clock (SSU) \$ynchronization (SEC/EEC) Link(s) Distribution to Other clocks outside the node **Node Clock** (SSU) **Network Element Clock**

#### SyncE: Introduction

- Several applications requiring accurate frequency are reached by Ethernet

- Since the very start of timing over packet network activities, it was proposed to use a synchronous Ethernet physical layer

- Not in contradiction with IEEE 802.3 (+/- 4.6 ppm within the +/-100 ppm and +/- 20 ppm)

- Only in full duplex mode (continuous signal required)

- Based on SDH specification (for interoperability and simplifying the standardization task)

- Synchronous Ethernet equipment equipped with a synchronous Ethernet Equipment Clock – EEC (G.8262). Synchronous Ethernet interfaces extract the received clock and pass it to the system clock.

- Synchronization Status Message as per G.8264

- Enhanced SyncE (G.8262.1)

- Generalized as physical layer based clock (SEC, Synchronous Equipment Clock)

- It does not transport Time

- but it was proposed

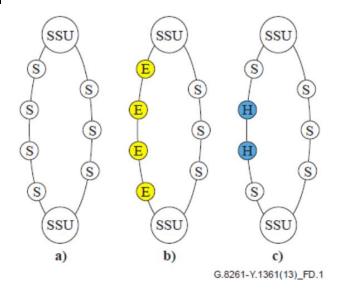

- All nodes must support SyncE: sync chain as per G.803

- Cannot be transported transparently across network boundaries

Figure 8-5/G.803 – Synchronization network reference chain

### SSM (Synchronization Status Message) in SyncE

- SSM required to prevent timing loops and to support reference selection (as per SDH)

- Details according to G.781 and G.8264

- In SDH SSM delivered in fixed locations of the SDH frame

- Packet based mechanism required in case of SyncE

- OUI (organizationally unique identifier) from IEEE reused to specify exchange of QLs

over the OAM specific slow protocol (OSSP)

- Option 1 clock treated as G.813option 1 (QL-SEC), Option 2 as an G.812type IV clock (QL-ST3)

G.8264-Y.1364(14)\_F11-1

- —Two types of protocol messages are defined

- "heart-beat" message (once per second)

- Event message generated immediately after a change in QL value

- —SSM QL value is considered failed if no SSM messages are received after a five second period

## Ethernet synchronization messaging channel (ESMC)

— ESMC PDU (Protocol Data Unit) with QL TLV always sent as the first TLV in the Data and padding field

| Octet number      | Size/bits         | Field                                                                    |          |                                                                                                  |                                           |                                 |  |

|-------------------|-------------------|--------------------------------------------------------------------------|----------|--------------------------------------------------------------------------------------------------|-------------------------------------------|---------------------------------|--|

| 1-6               | 6 octets          | Destination Address = 01-80-C2-00-00-02 (hex)                            |          |                                                                                                  |                                           |                                 |  |

| 7-12              | 6 octets          | Source Address                                                           |          |                                                                                                  |                                           |                                 |  |

| 13-14             | 2 octets          | Slow Protocol Ethertype = 88-09 (hex)                                    |          |                                                                                                  |                                           |                                 |  |

| 15                | 1 octet           | Slow Protocol Subtype = 0A (hex)                                         |          |                                                                                                  |                                           |                                 |  |

| 16-18             | 3 octets          | ITU-OUI = 00-19-A7 (hex)                                                 |          |                                                                                                  |                                           |                                 |  |

| 19-20             | 2 octets          | ITU Subtype                                                              | Oct      | et number                                                                                        | Size/bits                                 | Field                           |  |

| 21                | bits 7:4 (Note 1) | Version                                                                  |          | 1                                                                                                | 8 bits                                    | Type: 0x01                      |  |

|                   | bit 3             | Event flag                                                               |          | 2-3                                                                                              | 16 bits                                   | Length: 00-04                   |  |

|                   | bits 2:0 (Note 2) | Reserved                                                                 | 2-3      |                                                                                                  |                                           | Lengui. 00-04                   |  |

| 22-24             | 3 octets          | Reserved                                                                 |          | 4                                                                                                | bits 7:4 (Note)                           | 0x0 (unused)                    |  |

| 25-1532           | 36-1490 octets    | Data and padding (See point j)                                           |          |                                                                                                  | bits 3:0                                  | SSM code                        |  |

| Last 4            | 4 octets          | FCS                                                                      | NOTE Die | Bit 7 of octet 4 is the most significant bit. The least significant nibble, bit 3 to bit 0 (bits |                                           |                                 |  |

| number for the ES |                   | oit of octet 21. Bit 7 to bit 4 (bits 7:4) represent the four ereserved. |          | four-bit SSM code.                                                                               | ost significant off. The least significan | it mode, on 3 to on 0 (ons 3.0) |  |

- Recently extended to carry new clock types (and inform on PRTC traceability)

- Extended QL TLV

- Use of Padding bits also recently revised (set to all zero and ignored by receivers)

| Octet number | Size/bits | Field                                                                |       | Extended QL TLV             |                                     |                            |

|--------------|-----------|----------------------------------------------------------------------|-------|-----------------------------|-------------------------------------|----------------------------|

| 1            | 8 bits    | Type: 0x02                                                           |       |                             |                                     |                            |

| 2-3          | 16 bits   | Length: 0x0014                                                       |       |                             |                                     |                            |

| 4            | 8 bits    | Enhanced SSM code (see Table                                         | 11-6) |                             |                                     |                            |

| 5-12         | 64 bits   | SyncE clockIdentity of the originator of the extended QL TLV, Note1, |       |                             | SyncE clock follows the I           | Identity<br>EEE 1588 rules |

| 13           | 8 bits    | Flag; Note2                                                          |       |                             |                                     |                            |

| 14           | 8 bits    | Number of cascaded eEECs from the nearest SSU/PRC/ePRC               |       |                             |                                     |                            |

| 15           | 8 bits    | Number of cascaded EECs from the nearest SSU/PRC/ePRC                |       |                             |                                     |                            |

| 16-20        | 40 bits   | Reserved for future use                                              |       | Clock                       | Quality level                       | Enhanced SSM code          |

|              |           |                                                                      |       | EEC1                        | QL-EEC1                             | 0xFF                       |

|              |           |                                                                      | Othe  | EEC2                        | QL-EEC2                             | 0xFF                       |

|              |           |                                                                      |       | er clock types<br>contained | QL message<br>(refer to the QL TLV) | 0xFF                       |

|              |           |                                                                      |       | ITU-T G.781]                | Note 1                              |                            |

|              |           |                                                                      |       | Note 1                      |                                     |                            |

|              |           |                                                                      |       | PRTC                        | QL-PRTC                             | 0x20                       |

|              |           |                                                                      |       | ePRTC                       | QL-ePRTC                            | 0x21                       |

|              |           |                                                                      |       | eEEC                        | QL-eEEC                             | 0x22                       |

|              |           |                                                                      | ePRC  |                             | QL-ePRC                             | 0x23                       |

G.781]

Note 1: Tables 11-8 and 11-9 illustrate the full set of clock types from [ITU-T

**Field**

**Octet number**

Size/bits

#### SSM codes for SyncE

Table 11-7 (G.8264-2017): Option I

| Clock  | Quality  | SSM code | <b>Enhanced SSM</b> |

|--------|----------|----------|---------------------|

|        | level    |          | code                |

| PRC    | QL-PRC   | 0010     | 0xFF                |

| SSU-A  | QL-SSU-A | 0100     | 0xFF                |

| SSU-B  | QL-SSU-B | 1000     | 0xFF                |

| EEC1   | QL-EEC1  | 1011     | 0xFF                |

| Note 1 | QL-DNU   | 1111     | 0xFF                |

| PRTC   | QL-PRTC  | 0010     | 0x20                |

| ePRTC  | QL-ePRTC | 0010     | 0x21                |

| eEEC   | QL-eEEC  | 1011     | 0x22                |

| ePRC   | QL-ePRC  | 0010     | 0x23                |

Note 1: There is no clock corresponding to this quality level.

Note 2: When processing the SSM QL, The SSM code should be processed first, followed by processing the Enhanced SSM code.

If a clock supports both the QL TLV and the extended QL TLV, it should set the SSM code and the enhanced SSM code according to table 11-7/11-8, and send both the QL TLV and the extended QL TLV.

Table 11-8 (G.8264-2017): Option II

|        | •             | , , , , , , , , , , , , , , , , , , , |              |

|--------|---------------|---------------------------------------|--------------|

| Clock  | Quality level | SSM code                              | Enhanced SSM |

|        |               |                                       | code         |

| PRS    | QL-PRS        | 0001                                  | 0xFF         |

| Note 1 | QL-STU        | 0000                                  | 0xFF         |

| ST2    | QL-ST2        | 0111                                  | 0xFF         |

| TNC    | QL-TNC        | 0100                                  | 0xFF         |

| ST3E   | QL-ST3E       | 1101                                  | 0xFF         |

| ST3    | QL-ST3        | 1010                                  | 0xFF         |

| EEC2   | QL-EEC2       | 1010                                  | 0xFF         |

| Note 1 | QL-PROV       | 1110                                  | 0xFF         |

| Note 1 | QL-DUS        | 1111                                  | 0xFF         |

| PRTC   | QL-PRTC       | 0001                                  | 0x20         |

| ePRTC  | QL-ePRTC      | 0001                                  | 0x21         |

| eEEC   | QL-eEEC       | 1010                                  | 0x22         |

| ePRC   | QL-ePRC       | 0001                                  | 0x23         |

| N 4 TI |               |                                       | 1 1 1 1      |

Note 1: There is no clock that corresponds to this quality level.

Note 2: When processing the SSM QL, The SSM code should be processed first, followed by processing the Enhanced SSM code.

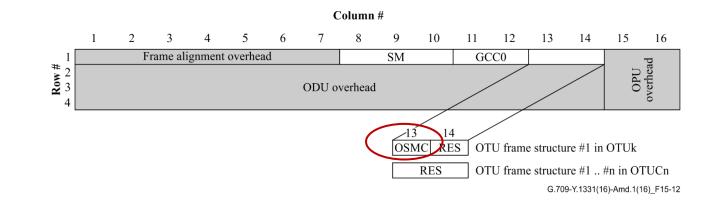

## Synchronization over OTN (Optical Transport Network)

- OSMC (OTN synchronization messaging channel) is used to carry

PTP and SSM messages

- Frequency synchronization can be carried over the physical layer, or via OTN clients (e.g., via SyncE)

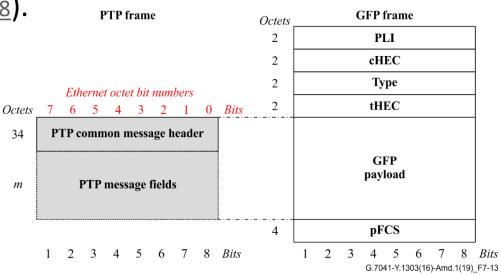

- Amendment to IEEE 1588 to support

PTP over OTN has been published

(IEEE 1588b-2022,

https://ieeexplore.ieee.org/document/9895348 .

- PTP over OTUk/FlexO, defined in G.7041 Clause 7.10

- GFP-F mapping

The header of GFP frame does not have source and destination MAC/IP address.

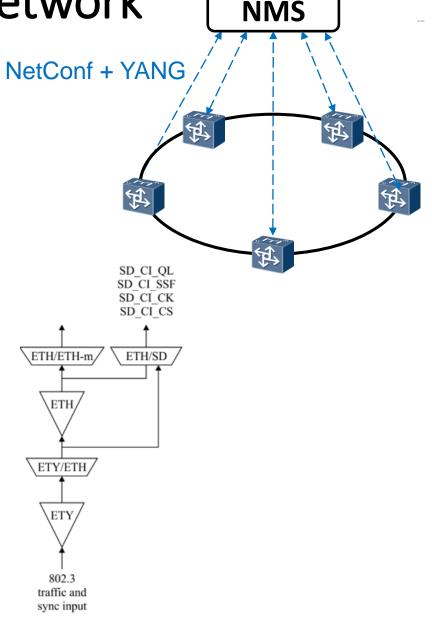

Managing Synchronization in the Network

- Managing the synchronization in the network is very important

- Management protocol between the equipment and Network management system (NMS) are important to be standardized to allow NMS to manage equipment from different vendors

- NetConf (IETF RFC 6241) + YANG (IETF RFC 6020) are suggested as management protocol

- —ITU-T Recommendations were updated to define new datasets and management objects

- —ITU-T G.781 defines the synchronization layer functions for frequency synchronization based on the physical layer

- It was updated to include physical layer (syncPHY) datasets

## Thank you!

Silvana Rodrigues

Senior Principal Engineering, Huawei Canada

Silvana.rodrigues@huawei.com

Stefano Ruffini

Strategic Technology Manager, Calnex Solutions

Stefano.ruffini@calnexsol.com